WhatApp/WeChat: 008618589033832

Skype: sannyduanbsp

Ba khía cạnh để đảm bảo tính toàn vẹn quyền lực trongThiết kế PCB

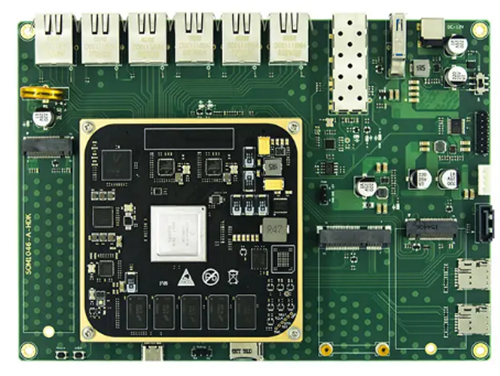

Trong thiết kế điện tử hiện đại, tính toàn vẹn năng lượng là một phần không thể thiếu của thiết kế PCB. Để đảm bảo hoạt động ổn định và hiệu suất của các thiết bị điện tử, chúng tôi phải xem xét và thiết kế toàn diện từ nguồn điện đến máy thu.

Thông qua việc thiết kế cẩn thận và tối ưu hóa các mô -đun năng lượng, các mặt phẳng lớp bên trong và chip cung cấp năng lượng, chúng ta có thể thực sự đạt được tính toàn vẹn của sức mạnh. Bài viết này sẽ đi sâu vào ba khía cạnh chính này để cung cấp hướng dẫn và chiến lược thực tế cho các nhà thiết kế PCB.

I. Hệ thống dây điện mô -đun nguồn

Mô -đun năng lượng là nguồn năng lượng của mọi thiết bị điện tử, hiệu suất và bố cục của nó ảnh hưởng trực tiếp đến sự ổn định và hiệu quả của toàn bộ hệ thống. Bố cục và định tuyến chính xác không chỉ có thể giảm nhiễu nhiễu mà còn đảm bảo dòng chảy trơn tru, do đó cải thiện hiệu suất tổng thể.

2. Bố cục mô -đun

1. Xử lý nguồn gốc:

Mô -đun năng lượng nên được chú ý đặc biệt vì nó đóng vai trò là điểm khởi đầu của công suất. Để giảm giới thiệu tiếng ồn, môi trường xung quanh mô -đun điện nên được giữ sạch nhất có thể để tránh sự lân cậntần số caohoặc các thành phần nhạy cảm với tiếng ồn.

2. Vượt qua chip cung cấp năng lượng:

Mô-đun năng lượng phải được đặt càng gần với chip được cung cấp năng lượng càng tốt. Điều này có thể làm giảm tổn thất trong quá trình truyền hiện tại và giảm các yêu cầu diện tích của mặt phẳng lớp bên trong.

3. Cân nhắc phân tán:

Mô -đun năng lượng có thể tạo ra nhiệt trong quá trình hoạt động, vì vậy cần đảm bảo rằng không có vật cản phía trên nó để tản nhiệt. Nếu cần thiết, tản nhiệt hoặc quạt có thể được thêm vào để làm mát.

4. Loopsing:

Khi định tuyến, tránh hình thành các vòng hiện tại để giảm khả năng nhiễu điện từ.

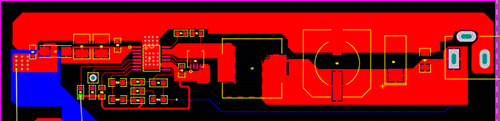

Ii. Lập kế hoạch thiết kế mặt phẳng lớp bên trong

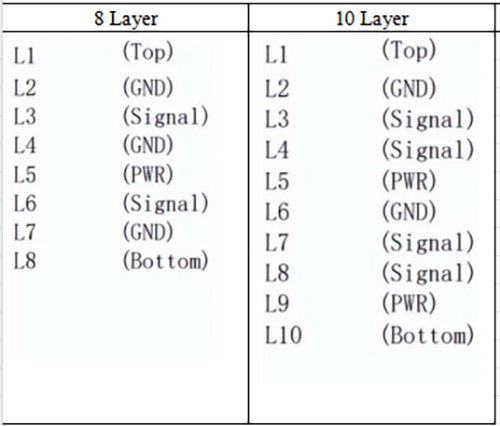

A. Thiết kế ngăn xếp lớp

In Thiết kế PCB EMC, Thiết kế ngăn xếp lớp là một yếu tố chính cần xem xét định tuyến và phân phối điện.

Một. Để đảm bảo các đặc tính trở kháng thấp của mặt phẳng công suất và hấp thụ khớp nối nhiễu mặt đất, khoảng cách giữa các mặt phẳng công suất và mặt đất không được vượt quá 10 triệu, thường được khuyến nghị là nhỏ hơn 5 triệu.

b. Nếu một mặt phẳng nguồn đơn không thể được thực hiện, một lớp bề mặt có thể được sử dụng để bố trí mặt phẳng nguồn. Các mặt phẳng và công suất liền kề chặt chẽ tạo thành một tụ điện mặt phẳng với trở kháng AC tối thiểu và các đặc tính tần số cao tuyệt vời.

c. Tránh hai lớp công suất liền kề, đặc biệt là với sự khác biệt điện áp lớn, để ngăn chặn khớp nối nhiễu. Nếu không thể tránh khỏi, hãy tăng khoảng cách giữa hai lớp công suất càng nhiều càng tốt.

d. Các mặt phẳng tham chiếu, đặc biệt là các mặt phẳng tham chiếu năng lượng, nên duy trì các đặc tính trở kháng thấp và có thể được tối ưu hóa thông qua các tụ điện bỏ qua và điều chỉnh lớp.

B.Multiple Phân đoạn năng lượng

Một. Đối với các nguồn năng lượng phạm vi nhỏ cụ thể, chẳng hạn như điện áp làm việc lõi của một chip IC nhất định, đồng phải được đặt trên lớp tín hiệu để đảm bảo tính toàn vẹn của mặt phẳng điện, nhưng tránh đặt đồng trên lớp bề mặt để giảm bức xạ nhiễu.

b. Việc lựa chọn chiều rộng phân đoạn nên phù hợp. Khi điện áp lớn hơn 12V, chiều rộng có thể là 20-30mil; Nếu không, chọn 12-20mil. Chiều rộng phân đoạn giữa các nguồn năng lượng tương tự và kỹ thuật số cần được tăng lên để ngăn sức mạnh kỹ thuật số can thiệp vào công suất tương tự.

c. Các mạng năng lượng đơn giản nên được hoàn thành trên lớp định tuyến và các mạng năng lượng dài hơn nên có các tụ lọc được thêm vào.

d. Mặt phẳng điện được phân đoạn nên được giữ thường xuyên để tránh các hình dạng không đều gây ra sự cộng hưởng và tăng trở kháng công suất. Các dải dài và hẹp và các phân chia hình quả tạ không được phép.

c.plane lọc

Một. Mặt phẳng điện nên được ghép nối chặt chẽ với mặt phẳng mặt đất.

b. Đối với các chip có tần số hoạt động vượt quá 500 MHz, chủ yếu dựa vào lọc tụ điện phẳng và sử dụng kết hợp lọc tụ điện. Hiệu ứng lọc cần được xác nhận bằng mô phỏng toàn vẹn sức mạnh.

c. Lắp đặt cuộn cảm cho các tụ điện tách trên mặt phẳng điều khiển, chẳng hạn như mở rộng các dẫn điện thoại và tăng các vias tụ điện, để đảm bảo rằng trở kháng mặt đất thấp hơn trở kháng mục tiêu.

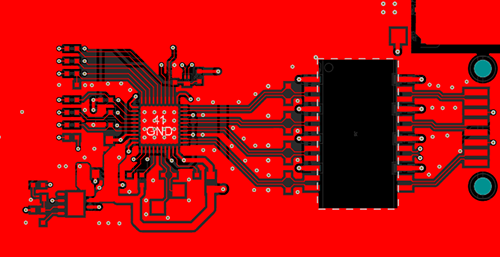

Iii. Dây bố trí chip nguồn

Chip Power là cốt lõi của các thiết bị điện tử và đảm bảo tính toàn vẹn năng lượng của nó là rất quan trọng để cải thiện hiệu suất và tính ổn định của thiết bị. Kiểm soát tính toàn vẹn công suất cho các chip công suất chủ yếu liên quan đến việc xử lý định tuyến các chân nguồn chip và bố cục chính xác và hệ thống dây điện của các tụ điện tách rời. Sau đây sẽ xem xét chi tiết và tư vấn thực tế về các khía cạnh này.

A.Chip Power Pin định tuyến

Việc định tuyến các chân công suất chip là một phần quan trọng của kiểm soát toàn vẹn sức mạnh. Để cung cấp một nguồn cung cấp ổn định, nên làm dày đường định tuyến của các chân điện, thường có cùng chiều rộng với các chân chip. Thông thường,chiều rộng tối thiểuKhông nên nhỏ hơn 8mil, nhưng để có kết quả tốt hơn, hãy cố gắng đạt được chiều rộng 10 triệu. Bằng cách tăng chiều rộng định tuyến, trở kháng có thể giảm, do đó giảm nhiễu công suất và đảm bảo nguồn cung cấp đủ cho chip.

B.Layout và định tuyến các tụ điện tách rời

Tụ điện tách rời đóng một vai trò quan trọng trong kiểm soát toàn vẹn công suất cho chip công suất. Tùy thuộc vào đặc điểm tụ điện và yêu cầu ứng dụng, các tụ điện tách rời thường được chia thành các tụ điện lớn và nhỏ.

Một. Tụ lớn: Tụ lớn thường được phân phối đều xung quanh chip. Do tần số cộng hưởng thấp hơn và bán kính lọc lớn hơn, chúng có thể lọc hiệu quả nhiễu tần số thấp và cung cấp nguồn điện ổn định.

b. Tụ nhỏ: Các tụ nhỏ có tần số cộng hưởng cao hơn và bán kính lọc nhỏ hơn, do đó chúng nên được đặt càng gần càng tốt với các chân chip. Đặt chúng quá xa có thể không lọc ra tiếng ồn tần số cao một cách hiệu quả, mất hiệu ứng tách rời. Bố cục chính xác đảm bảo rằng hiệu quả của các tụ nhỏ trong việc lọc nhiễu tần số cao được sử dụng đầy đủ.

C. Phương pháp phân tách song song

Để cải thiện hơn nữa tính toàn vẹn của sức mạnh, nhiều tụ tách rời thường được kết nối song song. Mục đích chính của thực tiễn này là giảm độ tự cảm loạt tương đương (ESL) của các tụ điện riêng lẻ thông qua kết nối song song.

Khi song song với nhiều tụ điện tách rời, cần chú ý đến việc đặt Vias cho các tụ điện. Một thực tế phổ biến là bù đắp cho vias của sức mạnh và mặt đất. Mục đích chính của điều này là để giảm độ tự cảm lẫn nhau giữa các tụ điện tách rời. Đảm bảo rằng độ tự cảm lẫn nhau nhỏ hơn nhiều so với ESL của một tụ điện duy nhất, do đó trở kháng ESL tổng thể sau khi song song với nhiều tụ điện tách rời là 1/n. Bằng cách giảm độ tự cảm lẫn nhau, hiệu quả lọc có thể được tăng cường một cách hiệu quả, đảm bảo cải thiện độ ổn định năng lượng.

Cách trình bàyvà định tuyến các mô -đun năng lượng, lập kế hoạch thiết kế mặt phẳng lớp bên trong và xử lý chính xác bố cục chip và hệ thống dây điện không thể thiếu trong thiết kế thiết bị điện tử. Thông qua bố cục và định tuyến thích hợp, chúng tôi có thể đảm bảo tính ổn định và hiệu quả của các mô -đun năng lượng, giảm nhiễu nhiễu và cải thiện hiệu suất tổng thể. Thiết kế ngăn xếp lớp và phân đoạn nhiều năng lượng tối ưu hóa hơn nữa các đặc điểm của các mặt phẳng năng lượng, giảm nhiễu nhiễu công suất. Xử lý đúng cách bố trí chip công suất và các tụ điện và tách rời là rất quan trọng để kiểm soát tính toàn vẹn công suất, đảm bảo nguồn cung cấp ổn định và lọc nhiễu hiệu quả, tăng cường hiệu suất và ổn định của thiết bị.

Trong hoạt động thực tế, các yếu tố khác nhau như cường độ hiện tại, chiều rộng định tuyến, số lượng vias, hiệu ứng khớp nối, v.v., cần được xem xét toàn diện để đưa ra bố cục hợp lý và quyết định định tuyến. Thực hiện theo các thông số kỹ thuật thiết kế và thực tiễn tốt nhất để đảm bảo kiểm soát và tối ưu hóa tính toàn vẹn của sức mạnh. Chỉ bằng cách này, chúng tôi mới có thể cung cấp nguồn điện ổn định và hiệu quả cho các thiết bị điện tử, đáp ứng nhu cầu hiệu suất ngày càng tăng và thúc đẩy sự phát triển và tiến trình của công nghệ điện tử.

Thâm Quyến Anke PCB Co., Ltd

Thời gian đăng: Mar-25-2024